DSD-3.1-FSM

FSM

introduction

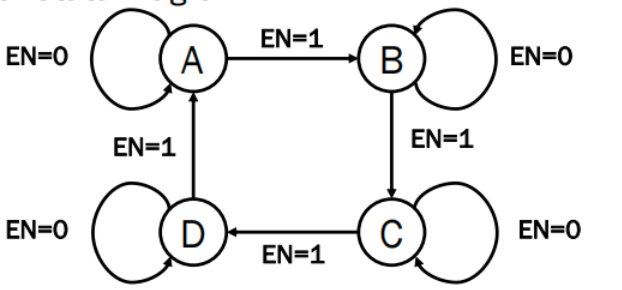

Finite state machines (FSMs) are mathematical abstractions that are used to solve a large variety of problems

Actually simple FSM design is just a step beyond the sequential circuit design

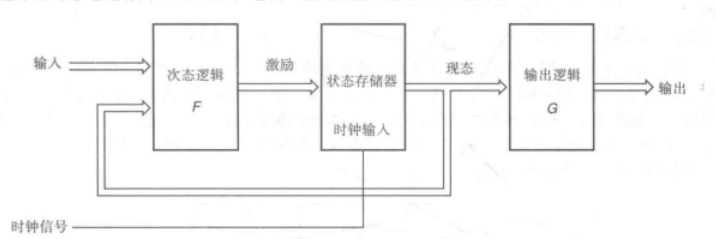

They are clocked synchronous sequential circuit 同步时序电路

The state only changes on clock edges 只在时钟边沿改变状态

They has only finite number of states. 拥有有限个状态

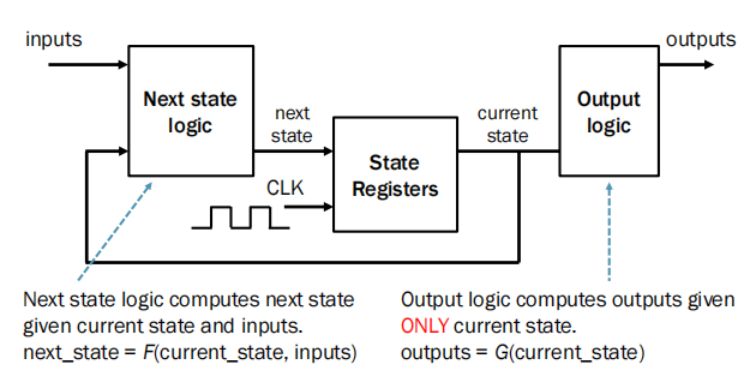

状态机分为Moore和Mealy

Moore Machines

一个时序电路输出同时取决于现态

next_state = F(current_state, inputs)

outputs = G(current_state)

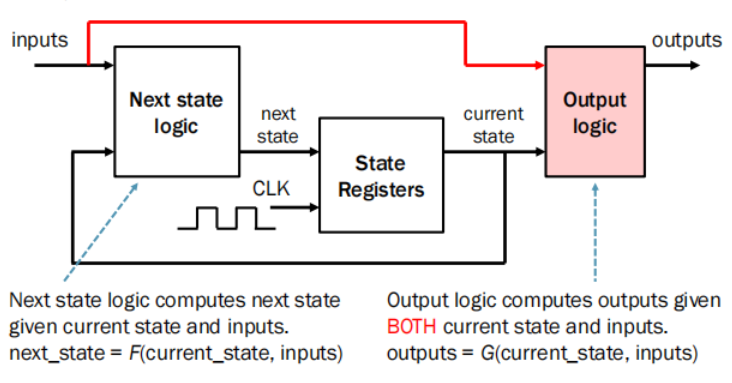

Mealy Machines

输出取决于现态和输入

next_state = F(current_state, inputs)

outputs = G(current_state, inputs)

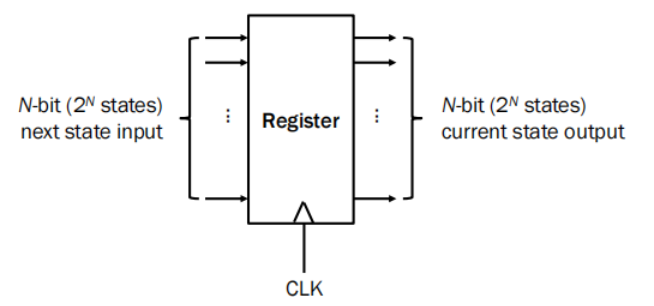

State Register

A state register with N flip-flops has 2N possible states

Designing a State Machine

\1. Start with specification

\2. Draw state diagram

\3. Formalise with state/output table

\4. Carry out state assignment

\5. Create state transition/output table

\6. Get minimised Boolean equations

\7. Synthesise circuit & optimise

这章笔记不太全,一部分手写了(字丑见谅):

链接:https://pan.baidu.com/s/14fmdxCFF8gPnUzrQqdOnMg?pwd=bupt

提取码:bupt