阻塞赋值和非阻塞赋值的应用场景

在Verilog HDL语言中,信号有两种赋值方式:

非阻塞(Non_Blocking)赋值方式( 如 b <= a; )

“阻塞”是指在进程语句(initial 和 always)中,当前的赋值语句会阻断其后语句的正常执行,也就是说后面的语句必须等到当前的赋值语句执行完毕才能执行。而且阻塞赋值可以看成是一步完成的,即:计算等号右边的值并同时赋给左边变量。

块结束后完成赋值(并不是立马改变值)

阻塞(Blocking)赋值方式( 如 b = a; )

“非阻塞”是指在进程语句(initial 和 always)中,当前的赋值语句不会阻断其后语句的正常执行。

b的值在赋值语句执行完后立刻就改变

在描述组合逻辑的always 块中用阻塞赋值,则综合成组合逻辑的电路结构。

在描述时序逻辑的always 块中用非阻塞赋值,则综合成时序逻辑的电路结构。

举例

module block(Clk,Rst_n,a,b,c,out);

input Clk;

input Rst_n;

input a,b,c;

output reg[1:0] out;

//用阻塞赋值

reg [1:0] d;

always@(posedge Clk or negedge Rst_n) begin

if(!Rst_n)

out= 2'b0;

else begin

d=a+b;

out=d+c;

end

end

endmodule我们想构建一个a+b+c的例子

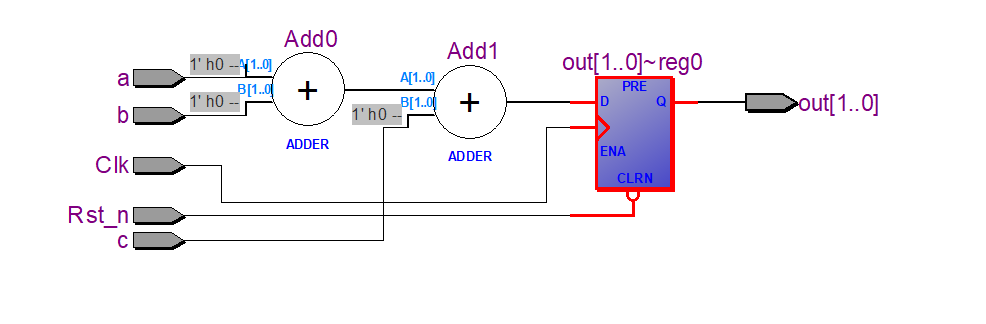

第一种方式:使用阻塞但按照运算顺序

d=a+b;

out=d+c;

系统综合出的电路如下:

可以看出add0和add1是组合逻辑,也就是a+b+c是一步完成的。

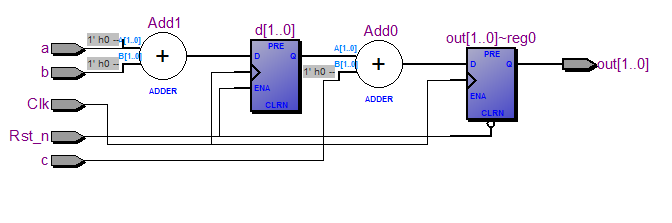

第二种方式:使用非阻塞赋值

非阻塞赋值顺序没有影响所以

d<=a+b;

out<=d+c;

此时生成的电路为

特殊情况,如果将阻塞赋值顺序反过来也会实现上图效果

不推荐使用

本博客所有文章除特别声明外,均采用 CC BY-NC-SA 4.0 许可协议。转载请注明来自 Chilh!

评论